Параллельные регистры

Параллельные

регистры - это устройства, предназначенные

для записи, хранения и выдачи информации, представленной в виде двоичных кодов. Для хранения каждого двоичного

разряда в регистре используется одна триггерная ячейка.

Для запоминания многоразрядных слов необходимое число

триггеров объединяют вместе и рассматривают как единый функциональный узел-регистр. Если регистр построен на

триггерах-защелках, то его называют регистр-защелка.

Типовыми внешними связями регистра являются информационные входы D;, вход сигнала записи (или

загрузки) С, вход гашения R, выходы триггеров Q. В

упрощенном варианте регистр может не иметь входа гашения и инверсных выходов.

На рис. 1

показана схема четырехразрядного регистра, выполненного на ИМС К155ТМ5 и

К155ЛИ1.

При подаче управляющего сигнала у1=1 информация по входам X1—Х4 записывается одновременно в соответствующие разряды четырех

D-триггеров. При y1=y2=0 информация хранится в

регистре памяти, а при y2=1

происходит параллельное считывание информации.

Рис.1. Четырехразрядный параллельный регистр

Условным изображением регистра по рис. 2, а пользуются тогда, когда на

схеме необходимо показать каждый вход и выход данных. Если же тракт данных

рассматривается как единое, укрупненное понятие - шина данных, то пользуются обозначением, показанным на рис 2, б.

а)

б)

Рис. 2. Условное обозначение регистра

Выпускаемые промышленностью регистры иногда объединяют на кристалле микросхемы

с другими узлами, в паре с которыми регистры часто используются в схемах

цифровой аппаратуры. Пример такого комплексного узла - микросхема

многорежимного буферного регистра (МБР) К589ИР12, основу которой составляет

8-разрядный регистр-защелка с входами DO—D7, С, R и восемью выходами Q0—Q7,

снабженными усилителями мощности (буферами) с тремя состояниями выхода. Кроме

того, в состав микросхемы входят несколько элементов управления. Усилители с

тремя состояниями выхода имеет и 4-разрядный регистр К155ИР15, построенный на

непрозрачных триггерах без свойств захвата или проницаемости, т. е. управляемых

строго фронтом.

Регистровая память

Существуют микросхемы, в которых регистр объединен с входным

мультиплексором, позволяющим принимать входные данные с двух и более

направлений, выбираемых сигналами на адресных входах микросхемы. Объединяют

регистр и с выходным демультиплексором, позволяющим передавать содержимое

регистра на различные направления.

Сразу несколько

регистров содержат микросхемы регистровой

памяти (register memory, register file, сверхоперативная память). Входы Di регистров подключены к общей входной

шине данных (data in). Вход загрузки требуемого

регистра выбирается дешифратором записи на основании поступающего на его вход

адреса записи (write address), т. е. кода номера

загружаемого регистра. Запись данных, присутствующих на шине, происходит в момент поступления

сигнала разрешения записи (write enable).

Выходы регистров мультиплексором подключаются к выходной

шине (data out). Номер регистра, с которого

происходит чтение, определяет код адреса чтения (read address). Выдачу данных разрешает сигнал разрешения чтения (read enable).

Поскольку дешифрация адреса записи и адреса чтения

производится двумя независимыми узлами, имеющими автономные адресные входы, регистровая память может одновременно

записывать число в один из регистров и читать число из другого.

Микросхемы регистровой памяти

легко наращиваются по разрядности и допускают наращивание по числу регистров.

Они разработаны для построения блоков регистров

общего назначения (РОН) и других специализированных блоков памяти

небольшого объема, предназначенных для временного хранения исходных данных и

промежуточных результатов в цифровом устройстве.

По мере увеличения числа регистров памяти разработчики

отказываются от независимой адресации регистров при записи и чтении. Остается

лишь один комплект адресных входов и один дешифратор адреса, которые

используются и при записи, и при считывании. Такую схему регистровой памятью

уже не называют. По ЕСКД она обозначается RAM (random access memory, т. е. память с

произвольным доступом). Используются также термины: запоминающее устройство с произвольной выборкой (ЗУПВ), оперативное запоминающее устройство

(ОЗУ), оперативная память, а иногда -

просто память. В микросхемах ЗУПВ ввод и вывод данных при записи и чтении могут

осуществляться через одни и те же выводы корпуса за счет использования в тракте

считывания элементов с тремя состояниями выхода или с открытым коллектором.

Режимы работы микросхемы запись, чтение

и хранение задаются комбинациями

сигналов на ее входах управления. Если для ввода данных при записи и вывода их при

чтении используются различные выводы корпуса (входы Di и выходы Qi), то режим хранения может

быть совмещен с режимом чтения.

Микросхемы ОЗУ малой емкости часто

выпускаются в составе распространенных серий. Они имеют входы адреса Аj, входы данных Di ; вход режима W/R: запись или чтение; выходы данных Qi; вход (или несколько конъюнктивных входов) разрешения Е, чаще называемый выбор кристалла ВК, выбор микросхемы ВМ или CS (chip select). Такую

микросхему можно рассматривать как группу регистров, дешифратор для их выборки,

цепи записи в регистры и считывания с них. Примерами подобных ИМС могут служить

К155РУ2 емкостью 16х4 (16 слов по 4 разряда), К537РУ8 – 2Кх 8. Такие ОЗУ

принято называть статическими. Наращивание разрядности и числа хранимых слов

производится, как и в случае ПЗУ.

Микросхемы ЗУПВ большей емкости

выпускают уже в составе определенных серий БИС памяти. Часто такие микросхемы

имеют временную диаграмму с большим числом регламентированных интервалов, адрес

может подаваться по частям, есть микросхемы, требующие регенерации хранимых

данных (динамические ОЗУ).

Сдвигающие регистры

Сдвигающий, или сдвиговый

регистр (shift register) это регистр, содержимое

которого при подаче управляющего сигнала СДВИГ может сдвигаться в сторону

старших или младших разрядов. Схема сдвигающего регистра из цепочки

непрозрачных триггеров показана на рис. 3.

Рис. 3. Сдвигающий регистр

Пусть на рисунке триггер Q0 – младший , Qm-1 – старший; вход каждого

триггера (кроме Q0) подключен к выходу соседнего младшего триггера. Когда

на все С входы триггеров поступает активный спад сигнала Shift, выход каждого триггера принимает состояние своего младшего соседа и,

таким образом, информация, содержащаяся в регистре, сдвигается на один разряд в

сторону старших разрядов, влево. Триггер Q0 принимает при этом

состояние последовательного входа DS (data serial). Информация, поступившая на вход DS во время какого-либо

такта, появится на выходе Qm-1 через m тактов.

Существенно, что в схеме

использованы именно непрозрачные триггеры. Если поставить прозрачные защелки,

то при активном уровне сигнала Shift все триггеры становятся

прозрачными, и сигнал DS успеет пройти столько

триггеров, сколько позволит длительность сигнала Shift .

Часто требуются более

сложные регистры: с параллельной синхронной записью информации, реверсивные, с

параллельно-последовательной записью. Такие регистры называются универсальными. Примером

такого регистра служит ИМС К155ИР11. Регистр может работать в четырех режимах:

параллельное занесение данных, сдвиг влево, сдвиг вправо, хранение данных.

Применения сдвиговых

регистров очень разнообразны.

В арифметике сдвиг числа

на один разряд влево соответствует умножению его на 2, сдвиг вправо – делению

пополам.

В аппаратуре передачи данных универсальные

регистры преобразуют параллельный код в последовательный и обратно. Передача

данных последовательным кодом по сравнению с передачей параллельным существенно

экономит число линий связи. Это покупается ценой увеличения времени обмена.

Общие

понятия

Счетчик - это устройство для подсчета числа

входных сигналов.

Как операционный элемент счетчик реализует

преобразование число- импульсного кода в позиционный по некоторому основанию

системы счисления. В ЭВМ счетчики используются для образования

последовательности адресов команд, для счета количества циклов выполнения

операций и т.д.

С точки зрения теории автоматов, счетчик - это цифровой

автомат, внутреннее состояние которого является функцией количества поступивших

входных сигналов.

Количество переключающих сигналов, которое надо подать на

вход счетчика для того чтобы счетчик вернулся в исходное состояние, равное

числу состояний счетчика, называется коэффициентом пересчета или модулем

счетчика – Ксч . Счетчик называется двоичным, если Ксч =

2m, где т - целое число, m>0, и

десятичным, если Ксч = 10p , где р - целое

число, р > 0. Счетчики чаще всего строятся на триггерах различных типов,

которые являются элементарными счетчиками с модулем 2.

Состояние счетчика в любой момент времени определяется кодом

Q , который зафиксирован на его триггерах. Задать правила

работы счетчика - значит тем или иным способом определить функцию Qn, = f(n), при п =0,1,2 ... Ксч , где Qn -

состояние счетчика после n-го входного переключающего сигнала, n -номер входного переключающего сигнала.

Очевидно, что Qp = Qp + Ксч

при любом n .

Любой счетчик с модулем Ксч может быть

использован как делитель частоты входных сигналов с коэффициентом деления Ксч

.

По порядку изменения состояний могут быть счетчики с

естественным и произвольным порядком счета. В первых счетчиках значение кода

каждого последующего состояния отличается на 1 от кода предыдущего состояния.

По способу переключения триггеров во время счета

счетчики делятся на асинхронные и синхронные. Первые называются еще счетчиками

с последовательным переносом, т.к. переход каждого триггера из одного состояния

в противоположное происходит последовательно во времени. Входной переключающий

сигнал непосредственно воздействует лишь на первый триггер, и каждый триггер

вырабатывает переключающий сигнал для следующего соседнего триггера.

Синхронные счетчики называются еще счетчиками с

параллельным переносом, т.к. в них входной переключающий сигнал непосредственно

воздействует на все триггеры счетчика, что обеспечивает одновременность

переходов триггеров.

Асинхронные счетчики

Рис. 4. Схема (а) и

временные диаграммы (6) двоичного

асинхронного суммирующего счетчика

На рис. 4, а изображен простейший способ включения триггеров, реализующий

последовательный суммирующий счетчик. Показан трехразрядный счетчик с

коэффициентом пересчета Ксч = 23 = 8, Следовательно, после подачи на

вход восьми импульсов счетчик возвратится к

исходному состоянию. Будем говорить, что подача на вход счетчика числа

импульсов, превышающего Ксч -1 (в данном примере 7 ), вызывает переполнение

счетчика.

Последовательный характер работы

является причиной двух недостатков последовательного счетчика: меньшая скорость счета по сравнению с

параллельными счетчиками и возможность появления ложных сигналов на выходе

схемы.

Допустимая скорость счета в счетчиках обоих типов

определяется максимальной скоростью переключения одного триггера.

Определяя максимальную скорость

счета последовательного счетчика, следует учитывать наиболее неблагоприятный

случай изменения состояния всех m триггеров.

Суммарную продолжительность переходного процесса можно определить как сумму

времен запаздывания отдельных элементов, соединяющих триггеры, и времен

срабатывания всех триггеров. Найденное таким образом максимальное время

перехода счетчика из одного состояния и другое следует считать предельным.

Обычно реальное время перехода меньше предельного, так как в ряду

последовательно включенных триггеров данный триггер начинает переход из одного

состояния в другое еще до окончания переходного процесса в возбуждающем его

элементе.

Последовательный характер

переходов триггеров счетчика является источником ложных сигналов на его

выходах. Например, в счетчике, ведущем счет в четырехразрядном двоичном коде с

«весами» 8-4-2-1, при переходе от числа 0111 к числу 1000 на выходе появится

следующая последовательность сигналов:

0111 ->0110 ->0100 ->0000

->1000.

Это означает, что при переходе из

состояния 7 в состояние 8 на выходах счетчика на короткое время появятся

состояния 6; 4; 0. Эти дополнительные состояния могут вызвать неправильную

работу других устройств.

Синхронные счетчики

С целью уменьшения времени протекания переходных процессов схему, показанную на

рис. 4, а, можно реализовать в

варианте с подачей входных импульсов одновременно на все триггеры. В этом

случае каждый триггер вырабатывает для всех последующих лишь сигналы

управления, являющиеся логической функцией состояния счетчика и определяющие

конкретные триггеры, которые изменяют состояние при данном входном импульсе.

Принцип формирования этих сигналов следует из временной диаграммы на рис.4,б

: триггер меняет состояние при

поступлении очередного счетного импульса , если все предыдущие триггеры

находились в состоянии 1. Отсюда и следует схема синхронного счетчика,

показанная на рис. 5.

Рис. 5. Четырехразрядный

синхронный счетчик

Быстродействие счетчика характеризуется разрешающим

временем, т.е. минимальным временным интервалом между входными сигналами, при

котором счетчик еще правильно функционирует. Максимальная частота счета Fmax связана с

разрешающим временем Тразр

простым соотношением: Fmax = Т -1разр .

Очевидно, что быстродействие синхронных счетчиков при прочих равных условиях

всегда выше, чем асинхронных.

Интегральные счетчики.

Интегральный двоичный асинхронный счетчик К155И.Е5

(рис.6) состоит из счетчика на 2 (триггер T1) и счетчика на 8 (триггеры Т2-Т4), соединение которых исходно

отсутствует. Установка "0" производится, когда на входах R1 и R2 одновременно "1". Во время

работы хотя бы на одном из входов должен быть "0". Для получения 4-х

разрядного счетчика внешней перемычкой соединяют выход Q0 со входом C2.

Десятичные счетчики строят обычно

на основе четырехразрядных двоичных счетчиков. Для того чтобы уменьшить Ксч

четырехразрядного счетчика с 16 до 10, вводят дополнительные логические связи.

При этом в зависимости от вида логической связи одним и тем же десятичным

числам в разных счетчиках могут соответствовать различные двоичные кодовые

комбинации или, иначе говоря, счетчики работают в различных двоично-десятичных

кодах.

Рис. 6. Структура счетчика К155ИЕ5

Схема на рис.7 соответствует десятичному счетчику К 155 ИЕ 2, работающему в коде 8-4-2-1. Счетчик

состоит из счетчика на 2 (триггер TI) и счетчика на 5 (триггеры Т2-Т4), соединение которых исходно

отсутствует. Для образования десятичного счетчика выводы Q0 и C2 соединяются между собой. Счетчик имеет входы нетактируемой

установки в "0" (0000) и в "9" (1001) - выводы R1,R2 и S1,S2. Во

время счета хотя 6ы на одной из

каждой пары входов должен быть "0".

Рис. 7. Структура счетчика К155ИЕ2

Условные обозначения асинхронных счетчиков К155ИЕ 5, К155ИЕ

2 и синхронных счетчиков К155ИЕ 7 и К155ИЕ 6 показаны на рис.8

Рис.8. Условные

обозначения счетчиков.

К155ИЕ7. интегральный реверсивный двоичный синхронный

счетчик имеет два счетных входа: вход суммирования +1 и вход вычитания –1.

Если все триггеры находятся в состоянии "1", то

при приходе импульса на вход суммирования (+1) формируется сигнал

"переноса" ( ( 15 ).

Импульс на входе (-1), если все триггеры находятся в состоянии "0",

формирует сигнал "заема" ( 0). Эти сигналы используются для

увеличения разрядности счетчиков.

К155ИЕ6 –синхронный реверсивный десятичный счетчик,

работающий в коде 8-4-2-1. Кроме двоичных реверсивных межтриггерных связей, в

счетчике KI55 ИЕ б

существуют дополнительные логические цепи, обеспечивающие недвоичный переход от

кода 1001 к коду 0000 при суммировании и обратный переход при вычитании.

Сброс счетчиков KI55 ИЕ 6 и К155

ИЕ 7 производится сигналом "1", подаваемом на вход R Во время счета

на этом выводе должен быть "0".

В обоих счетчиках триггеры имеют

входы предварительной установки D, тактируемые

потенциалом. В режиме счета сигнал на входе С (вывод 11) равен "1",

цепи предустановки отключены. Если на входе С "0", то триггеры

устанавливаются в состояния, соответствующие сигналам, поданным на входы D0 , D1 , D2 , D3. Естественно, что сигнал переноса в счетчике К 155 ИЕ 6

возникает на выходе ( 9) при состоянии счетчика 1001 и поступлении следующего

счетного импульса.

Счетчики с различными коэффициентами

пересчета.

Счетчики с коэффициентами

пересчета, отличающимися от двоичных и десятичных, могут быть также построены

путем введения дополнительных связей в двоичные счетчики.

Однако существуют и общие методы

построения счетчиков с любым заданным Ксч. Один из этих методов

заключается в немедленном сбросе в "0"

счетчика, установившегося в комбинацию, соответствующую числу Ксч . Если, например, нам нужно построить

счетчик на 5, то, сбрасывая двоичный трехразрядный счетчик на "0"

каждый раз, когда он будет принимать состояние 101, мы обеспечим возврат счетчика в исходное состояние после каждых

пяти входных импульсов.

Подобный прием удобно применять при использовании счетчиков,

имеющих элементы " И "на

входах установки в "0" (К155ИЕ 5 и К155ИЕ 2) и в "9"

(К155ИЕ 2). В качестве примера на рис.9 показаны соединения для получения Ксч

= 10 для счетчика К155ИЕ 5 и Ксч = 7 для счетчика KI55ИЕ 2. В последнем случае

из десяти состояний исключается три состояния (0110, 0111 и 1000).

При использовании синхронных счетчиков К155ИЕ б и К155ИЕ 7

для построения счетчиков с различными Ксч может использоваться метод

начальной установки. Этот метод заключается в том, что счет каждый раз

начинается не с нуля, как обычно, а с некоторого числа. Оно и определяет Ксч

.

Рис.9. а) Ксч

= 10; б) Ксч = 7

Применение счетчиков

1) Счетчик

событий.

События

должны быть представлены импульсами с соответствующими логическими уровнями.

Максимальное число событий должно быть не более Ксч -1, иначе произойдет

переполнение счетчика.

2) Делитель частоты

импульсов.

Любой

счетчик с модулем Ксч

может быть использован как делитель частоты входных сигналов

с коэффициентом деления Ксч .

Если

частота и период импульсов на входе счетчика Fвх и Tвх, то частота импульсов на выходе

старшего триггера Fвых

= Fвх

/ Kсч

, а их период Tвых

= Kсч

. Tвх.

3) Счетчик команд (СК)

в процессоре ЭВМ.

В

качестве СК используется двоичный счетчик, разрядность которого равна

разрядности шины адреса (ША), т.к. выходы его триггеров это линии адреса

соответствующего разряда. СК должен иметь возможность не только

последовательного счета, но и любого изменения текущего состояния для

реализации условных и безусловных переходов в исполняемой программе.

4) Распределители

импульсов (РИ).

РИ – устройство, распределяющее поток импульсов

последовательно, импульс за импульсом, по нескольким выходам. Одно из главных

применений РИ – системы обегающего контроля, где РИ управляют поочередным

подключением однотипных датчиков ко входу измерителя .

РИ могут строиться по различным схемам. Чаще всего это двоичный счетчик с

дешифратором (ДШ). Счетчик последовательно перебирает двоичные коды, ДШ в

соответствии с ними последовательно возбуждает свои выходы. При этом нужно

помнить, что ДШ будет расшифровывать не только верные, установившиеся состояния

счетчика, но и неустановившиеся, ложные. В результате на выходах такого РИ

кроме нормальных сигналов будут появляться короткие всплески напряжения (у ДШ с

прямыми выходами) или короткие провалы до нуля (у ДШ с инверсными выходами).

Эти сигналы отсутствуют при использовании синхронных счетчиков или их можно

устранить, стробируя ДШ по входам разрешения и запрещая его работу на время

существования ложного состояния счетчика.

Роль распределителя импульсов может выполнять и сдвиговый регистр

с единственной двигающейся единицей.

ЗУ предназначено для приема, хранения и выдачи

информации, представленной двоичным кодом.

БИС ЗУ условно

подразделяют на 2 класса:

1- оперативные ЗУ (ОЗУ);

2- постоянные ЗУ (ПЗУ).

БИС ОЗУ – предназначены для

построения основной памяти цифровых систем, в которой хранятся программы и

массив данных, определяющие текущий процесс обработки информации.

Отдельную группу

в этом классе составляют сверхоперативные ЗУ (СОЗУ), быстродействие которых

соответствует скорости работы процесса система.

ПЗУ – служат для хранения

информации, содержание которой не изменяется в процессе работы системы. ПЗУ

предназначены для хранения постоянных массивов информации – стандартных

подпрограмм и микропрограмм, преобразователей кодов, генераторов символов,

констант, табличных значений различных функций и т.п.

В зависимости от

способа занесения информации, т.е. программирования, различают три основные

разновидности БИС ПЗУ:

1. ПЗУ с

масочным программированием (фотошаблонами) (ПЗУМ)

2. Электрически

программируемые ПЗУ (пережигание перемычек током) (ППЗУ)

3.

Репрограммируемые ПЗУ (ультрафиолетом, запись и стирание током) (РПЗУ)

БИС ОЗУ и ПЗУ

состоят из накопителя информации (НК) и схем управления (СУ).

НК предназначен

для хранения информации и представляет собой матрицу ЗЭ, реализуемых на

логических схемах или отдельных транзисторах (диодах).

В качестве схем

управления применяют дешифраторы (ДШ), адресные формирователи, усилители считывания

и записи, схемы синхронизации и местного управления, а также схемы,

обеспечивающие согласование БИС ЗУ по логическим уровням с другими типами ИММС

(ТТЛ, И2Л, ЭСЛ и др.)

По принципу

построения НК информации БИС ЗУ строятся со словарной организацией (однокоординатной

выборкой) или матричной организацией (двухкоординатной выборкой).

Метод словарной

организации выборки применим только в БИС с небольшим кол-вом ЗЭ, что

обусловлено сложностью построения ДШ с числом входов, равным числу ЗЭ.

Как известно, ЗУ

служат не только для хранения информации, но и для обмена ею с другими цифр.

устр-вами.

Важнейшие

параметры

при организации ЗУ находятся в противоречии. Так, например, большая информац.

емкость не сочетается с высоким быстродействием, а быстродействие, в свою

очередь, не сочетается с низкой стоимостью.

В иерархии

памяти ЭВМ можно выделить следующие организационные уровни:

– Регистровые

ЗУ, находящиеся в составе микропро-цессора или других устр-в.

– Кэш-память –

служащая для хранения копий информации, используемых в текущих операциях

обмена. Высокое быстродействие кэш-памяти повышает производительность ЭВМ

(кэш-память может принадлежать и МП).

– Основная

память (ОЗУ, ПЗУ) – работающая в режиме непосредственного обмена с процессором

и по возможности согласованная с ним по быстродействию. Исполняемый в настоящий

момент фрагмент программы обязательно находится в основной памяти.

– Специализированные

виды памяти, характерные для некоторых специфическиих архитектур (буферная,

ассоциативная, видеопамять и другие)

– Внешняя

память – это ЗУ для хранения больших объемов информации. Обычно эта память

реализуется на основе устр-в с подвижным носителем информации (магнитные,

оптические, магнито-оптические и др.).

Организац. параметры ЗУ

– Инф. емкость –

max возм. объем хранимой информации. Выражается в битах или

словах. Бит хранится запоминающим элементом (т.е., например, триггером), а

слово или слова (8, 16, 32, 64, 128 и больше бит) – запоминающей ячейкой

(модулем) или группой ЗЯ, к которым возможно лишь одновременное обращение.

Добавление к единице измерения множителя "К" (кило) означает

умножение на 210 = 1024, а множителя "М" (мега) –

умножение на 220 = 1048576.

– Организационная

емкость ЗУ – это произведение числа хранимых слов (строк) – на их

разрядность.

– Быстродействие

ЗУ оценивают временем считывания, записи и длительностью циклов

чтения/записи.

Основные организационные

структуры ЗУ

Для статических

ПЗУ и ОЗУ характерны следующие структуры: 2D, 3D, 2DM.

Структура

2D

Рис. 10.

Структура ЗУ типа 2D.

.

В структуре 2D ЗЭ

организованы в прямоугольную матрицу размерностью M=K · m, где M – информационная емкость

памяти, K – число хранимых слов или число строк, m – их

разрядность.

Дешифратор (DC, ДШ)

адресного кода при наличии разрешающего сигнала "CS" (сигнала выборки

микросхемы) активизирует одну из выходных линий, разрешая одновременный доступ

ко всем элементам выбранной строки, хранящей слово, адрес которого

соответствует номеру строки. Элементы одного столбца соединены вертикальной

линией (внутренней линией данных, иначе называемой разрядной шиной (РШ)

записи/считывания). Элементы столбца хранят одноименные биты всех слов.

Направление обмена определяется усилителями чтения, записи под

воздействием сигнала RW (Read –

чтение,Write –

запись).

Недостатком

структуры 2D является то, что с ростом емкости памяти чрезмерно

усложняется дешифратор адреса, т.к. число выходов ДШ равно числу хранимых слов.

Например, для хранения 1 Кбит требуется ДШ с 1024 выходами.

Структура

3D

Структура 3D

позволяет резко упростить дешифраторы адреса с помощью двухкоординатной выборки

запоминающих элементов. Принцип 2х-координатной выборки поясняет

рис. 11 на примере ПЗУ, реализующего только операции чтения данных. Здесь код

адреса разрядностью "n" делится на две

половины, каждая из которых декодируется отдельно дешифраторами DCy DCx. В этой схеме выбирается

ЗЭ, находящийся на пересечении активных выходов обоих дешифраторов (например,

ЗЭ22 заштрихован). Таких

пересечений будет как раз 2n/2 × 2n/2 = 2n.

Рис. 11.

Структура ЗУ типа 3D.

При этом

суммарное число выходов обоих дешифраторов составляет 2n/2 + 2n/2 = 2n/2+1.

Например, если n = 210

= 1024, то 25 + 25 = 32 + 32 = 64 = 26, т.е. 26 = 25+1 (2n/2+1), что гораздо меньше, чем 2n

при реальных значениях "n".

Таким образом,

если для структуры 2D при хранении 1К слов потребовался бы ДШ с 1024

входами, тогда как для структуры типа 3D нужны 2 ДШ с 32 выходами

каждый. Недостатком структуры 3D в первую очередь является

усложнение элементов памяти, имеющих 2х-координатную выборку.

Структура

2DM

Структуры типа 3D имеют,

как и структуры типа 2D, довольно ограниченное применение, поскольку в

структурах типа 2DM (2D модифицированная)

сочетаются достоинства обеих рассмотренных структур – упрощается дешифрация

адреса и не требуетются ЗЭ с 2х-координатной выборкой.

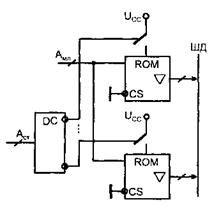

ЗУ типа ROM (рис.

12) структуры 2DM для

матрицы запоминающих элементов с

адресацией от дешифратора DCx имеет характер структуры 2D: возбужденный выход дешифратора выбирает целую строку. Однако в отличие от структуры 2D, длина строки не равна разрядности хранимых

слов, а многократно ее превышает. При этом число

строк матрицы уменьшается и, соответственно, уменьшается число выходов

дешифратора. Для выбора одной из строк

служат не все разряды адресного кода, а их часть Аn-1...Аk. Остальные разряды адреса

(от Аk-1 до А0)

используются, чтобы выбрать необходимое слово из того

множества слов, которое содержится в строке. Это выполняется с помощью

мультиплексоров, на адресные входы которых подаются коды Ak-1...А0. Длина строки равна m2k, где m — разрядность хранимых слов. Из каждого

"отрезка" строки длиной 2к мультиплексор выбирает один бит. На выходах мультиплексоров формируется выходное слово. По разрешению сигнала CS, поступающего на входы ОЕ управляемых буферов с тремя состояниями, выходное слово передается на

внешнюю шину.

На рис. 13 в более общем виде структура 2DM показана для ЗУ типа RAM с операциями чтения и записи. Из матрицы М по-прежнему

считывается "длинная" строка.

|

Рис. 12. Структура ЗУ типа 2DM

для ROM

|

Рис. 13. Структура ЗУ типа 2DM для RAM

Данные в нужный отрезок этой строки записываются (или

считываются из нее) управляемыми буферами данных

BD, воспринимающими выходные сигналы второго дешифратора DCy, и выполняющими не только функции мультиплексирования,

но и функции изменения направления передачи данных под воздействием

сигнала R/W (чтение/запись).

(ROM(M), PROM, EPROM, EEPROM)

Запоминающие устройства типа ROM (память только для чтения) хранят информацию, которая либо вообще

не изменяется (в ЗУ типов ROM(M) и PROM), либо

изменяется редко и не в оперативном режиме (в ЗУ типов EPROM и EEPROM).

В масочные ЗУ типа ROM(M) информация записывается при изготовлении

микросхем на промышленных предприятиях с помощью шаблона (маски) на завершающем

этапе технологического процесса.

ЗУ типа PROM программируются

после изготовления их предприятием электронной промышленности в лабораториях

потребителей без использования сложных технологических процессов. Для этого

используются несложные устройства (программаторы).

Программирование постоянной памяти заключается в том или ином

размещении элементов связи между горизонтальными и вертикальными линиями

матрицы запоминающих элементов.

Запоминающие устройства типа ROM имеют многоразрядную организацию (чаще всего 8-разрядную или

4-разрядную, для некоторых ИС 16-разрядную) и обычно выполняются по структуре 2DM. Простейшие ЗУ могут иметь структуру 2D. Технологии изготовления постоянных ЗУ

разнообразны – ТТЛ(Ш), КМОП, n-МОП и др.

Масочные

ЗУ

Элементом связи в масочных ЗУ могут быть диоды, биполярные

транзисторы, МОП-транзисторы и т. д.

В

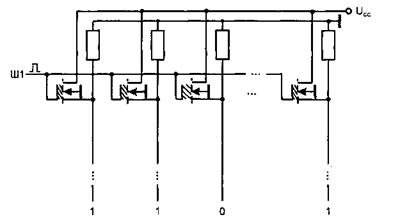

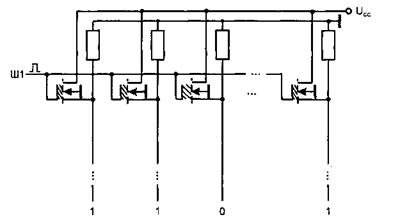

матрице диодного ROM(M) (рис. 14) горизонтальные

линии являются линиями выборки слов, а вертикальные – линиями считывания. Считываемое

слово определяется расположением диодов в узлах координатной сетки. При наличии

диода высокий потенциал выбранной горизонтальной линии передается на

соответствующую вертикальную линию, и в данном разряде слова появляется сигнал

логической единицы. При отсутствии диода потенциал близок к нулевому, т. к.

вертикальная линия через резистор связана с землей. В изображенной матрице при

возбуждении линии выборки Ш1 считывается слово 11010001 (в ячейке

номер один хранится это слово). При возбуждении Ш2 считывается слово 10101011

(оно хранится в ячейке номер 2). Шины выборки являются выходами дешифратора

адреса, каждая адресная комбинация возбуждает свой выход дешифратора, что

приводит к считыванию слова из адресуемой ячейки.

В матрице с диодными элементами в одних узлах матрицы диоды

изготовляются, в других – нет. При этом, чтобы удешевить производство, при

изготовлении ЗУ стремятся варьировать только один шаблон, так чтобы одни

элементы связи были законченными и работоспособными, а другие – незавершенными

и как бы отсутствующими. Для матриц с МОП-транзисторами часто в

МОП-транзисторах, соответствующих хранению нуля, увеличивают толщину

подзатворного окисла, что ведет к увеличению порогового напряжения транзистора.

В этом случае рабочие напряжения ЗУ не в состоянии открыть транзистор.

Постоянно закрытое состояние транзистора аналогично его отсутствию. Матрица с МОП-транзисторами

показана на рис. 15.

Рис.

14. Матрица диодных

запоминающих элементов

Рис.

14. Матрица диодных

запоминающих элементов

Рис. 15. Матрица МОП-транзисторных

элементов

ЗУ с масочным программированием отличаются компактностью

запоминающих элементов и, следовательно, высоким уровнем интеграции. При

больших объемах производства масочное программирование предпочтительно, однако

при недостаточной тиражности ЗУ затраты на проектирование и изготовление

шаблона для технологического программирования ЗУ окажутся чрезмерно высокими.

Отсюда видна и область применения масочных ЗУ – хранение стандартной

информации, имеющей широкий круг потребителей. В частности, масочные ЗУ имеют в

качестве "прошивки" коды букв алфавитов (русского и латинского),

таблицы типовых функций (синуса, квадратичной функции и др.), стандартное

программное обеспечение и т. п.

ЗУ типа PROM

В ЗУ типа PROM микросхемы

программируются устранением или созданием специальных перемычек. В исходной

заготовке имеются (или отсутствуют) все перемычки. После программирования

остаются или возникают только необходимые.

Устранение части перемычек свойственно ЗУ с плавкими перемычками

(типа fuse – предохранитель). При этом в исходном

состоянии ЗУ имеет все перемычки, а при программировании часть их ликвидируется

путем расплавления импульсами тока достаточно большой амплитуды и длительности.

В

ЗУ с плавкими перемычками эти перемычки включаются в электроды диодов или

транзисторов. Перемычки могут быть металлическими (вначале изготовлялись из

нихрома, позднее из титановольфрамовых и других сплавов) или

поликристаллическими (кремниевыми). В исходном состоянии запоминающий элемент

хранит логическую единицу, логический нуль нужно записать, расплавляя

перемычку.

Создание

части перемычек соответствует схемам, которые в исходном состоянии имеют

непроводящие перемычки в виде пары встречно включенных диодов или тонких

диэлектрических слоев, пробиваемых при программировании с образованием

низкоомных сопротивлений. Схемы с тонкими пробиваемыми диэлектрическими

перемычками наиболее компактны и совершенны. Их применение характерно для

программируемых логических СБИС.

Второй

тип запоминающего элемента PROM – два встречно включенных

диода. В исходном состоянии сопротивление такой цепочки настолько велико, что

практически равноценно разомкнутой цепи, и запоминающий элемент хранит

логический нуль. Для записи единицы к диодам прикладывают повышенное

напряжение, пробивающее диод, смещенный в обратном направлении. Диод

пробивается с образованием в нем короткого замыкания и играет роль появившейся

проводящей перемычки.

Запоминающие

элементы с плавкими перемычками и парами диодов показаны на рис. 16, а, б в исходном

состоянии и после программирования.

(а) (б)

Рис. 16.

Запоминающие элементы с плавкими перемычками (а) и диодными парами (б)

Матрица

запоминающих элементов ЗУ с плавкими перемычками в технике ТТЛ показана на рис.

17. ЗУ имеет организацию 32x8. Матрица содержит 32 транзистора с 9 эмиттерами в

каждом (8 рабочих и один технологический для уточнения режима прожигания,

технологический эмиттер на рисунке не показан). Высокий потенциал на какой-либо

шине выборки активизирует соответствующий транзистор, работающий в режиме

эмиттёрного повторителя. До программирования транзисторы передают высокий

потенциал базы на все выходные (разрядные) линии, т. е. по всем адресам

записаны слова, состоящие из одних единиц. Пережигание перемычки в цепи

какого-либо эмиттера дает ноль в данном разряде слова, например, для ячейки с

номером 1 показан вариант программирования для хранения по этому адресу слова

10100101. Выходы матрицы связаны с внешними цепями через буферные каскады,

имеющие выходы типа ОК или ТС. ЗУ имеет структуру 2D.

Рис. 17.

Матрица запоминающих элементов с плавкими перемычками в технике ТТЛ

Программирование

ЗУ с плавкими перемычками реализуется простыми аппаратными средствами и

может быть доступно схемотехникам даже при отсутствии специального

оборудования. На рис. 18 показан многоэмиттерный транзистор (МЭТ) с плавкими

перемычками и дополнительными элементами, обеспечивающими программирование ЗУ.

Выходы этого запоминающего элемента передаются во внешние цепи через буферные

каскады с тремя состояниями, работа которых разрешается сигналом ОЕ. При этом

сигнал разрешения работы формирователей импульсов программирования ОЕр

отсутствует, и они не влияют на работу схемы. При программировании буферы

данных переводятся в третье состояние (ОЕ = 0), а работа формирователей F

разрешается. Слово, которое нужно записать в данной ячейке, подается на линии

данных D7...D0. Те разряды слова, в которых имеются единицы, будут

иметь на выходах формирователей низкий уровень напряжения. Соответствующие

эмиттеры МЭТ окажутся под низким напряжением и через них пройдет ток прожигания

перемычки. При чтении отсутствие перемычки даст нулевой сигнал на вход буфера

данных. Так как буфер инвертирующий, с его выхода снимется единичный сигнал,

т.е. тот, который и записывался. Адресация программируемой ячейки как обычно обеспечивается

дешифратором адреса, подающим высокий уровень потенциала на базу адресуемого

МЭТ.

Рис. 18. Схема

запоминающей ячейки с элементами программирования плавких перемычек

Для прожигания перемычек на них подают токи в

десятки миллиампер в виде серии импульсов (для большей надежности прожигания).

Не все перемычки удается пережечь надлежащим образом, коэффициент

программируемости для серии К.556, например, составляет 0,5...0,7. В ЗУ с

плавкими перемычками возможно восстановление проводимости перемычек через некоторое

время из-за миграции в электроматериалах.

Плавкие

перемычки занимают на кристалле относительно много места, поэтому уровень

интеграции ЗУ с такими перемычками существенно ниже, чем у масочных ЗУ. В то же

время простота программирования пользователем и невысокая стоимость в свое

время обусловили широкое распространение ЗУ типа PROM. Невысокая стоимость

программируемых пользователем ЗУ объясняется тем, что изготовитель выпускает

микросхемы без учета конкретного содержимого ЗУ, т. е. освобожден от

проектирования по специализированным заказам и, следовательно, связанных с

этим затрат.

Внешняя

организация памяти типов ROM(M) и PROM проста: входными сигналами

для них служат адресный код и сигнал выбора микросхемы CS. Во времени последовательность

сигналов следующая: вначале подается адресный код (чтобы произошла дешифрация

адреса и было исключено обращение к непредусмотренной ячейке), затем поступает

сигнал выбора микросхемы CS и после задержки,

определяемой быстродействием схемы, на выходах данных устанавливаются

правильные значения считываемых сигналов.

ЗУ типов EPROM и EEPROM

В

репрограммируемых ЗУ типов EPROM и EEPROM (или E2PROM)

возможно стирание старой информации и замена ее новой в результате специального процесса, для проведения которого ЗУ выводится из

рабочего режима. Рабочий режим (чтение данных) – процесс, выполняемый с

относительно высокой скоростью. Замена же содержимого памяти требует выполнения

гораздо более длительных операций.

По способу стирания старой информации различают ЗУ со стиранием

ультрафиолетовыми лучами (EPROM или в русской

терминологии РПЗУ-УФ, т. е. репрограммируемые ПЗУ с ультрафиолетовым стиранием)

и электрическим стиранием (E2PROM или РПЗУ-ЭС).

Запоминающими элементами современных РПЗУ являются транзисторы

типов МНОП и ЛИЗМОП (добавление ЛИЗ к обозначению МОП происходит от

"Лавинная Инжекция Заряда").

МНОП-транзистор отличается от обычного МОП-транзистора двухслойным

подзатворным диэлектриком. На поверхности кристалла расположен тонкий слой

двуокиси кремния SiO2, далее более

толстый слой нитрида кремния Si3N4 и затем уже затвор (рис. 19). На

границе диэлектрических слоев возникают центры захвата заряда. Благодаря туннельному эффекту, носители заряда могут

проходить через тонкую пленку окисла толщиной не более 5 нм и скапливаться на

границе раздела слоев. Этот заряд и является носителем информации, хранимой

МНОП-транзистором. Заряд записывают созданием под затвором напряженности

электрического поля, достаточной для возникновения туннельного перехода

носителей заряда через тонкий слой SiO2. На границе раздела диэлектрических слоев можно создавать

заряд любого знака в зависимости от направленности электрического поля в

подзатворной области. Наличие заряда влияет на пороговое напряжение

транзистора.

Рис. 19.

Структура транзистора типа МНОП

Для МНОП-транзистора с n-каналом

отрицательный заряд на границе раздела слоев повышает пороговое напряжение

(экранирует воздействие положительного напряжения на затворе, отпирающего

транзистор). При этом пороговое напряжение возрастает настолько, что рабочие

напряжения на затворе транзистора не в состоянии его открыть (создать в нем

проводящий канал). Транзистор, в котором заряд отсутствует или имеет другой

знак, легко открывается рабочим значением напряжения. Так осуществляется хранение

бита в МНОП: одно из состояний трактуется как отображение логической единицы,

другое – нуля.

При программировании ЗУ используются относительно высокие

напряжения, около 20 В. После снятия высоких напряжений туннельное прохождение

носителей заряда через диэлектрик прекращается и заданное транзистору пороговое

напряжение остается неизменным.

После 104…106 перезаписей

МНОП-тр-р перестает устойчиво хранить заряд. РПЗУ на МНОП-тр-х энергонезависимы

и могут хранить информацию в течение долгого времени.

Перед новой записью старая информация стирается

записью нулей во все запоминающие элементы.

Транзисторы типа ЛИЗМОП

ЛИЗМОП всегда имеет так называемый плавающий затвор,

который может быть единственным или вторым, дополнительным к обычному

(управляющему) затвору.

Транзисторы с одним плавающим затвором используются в

ЗУ типа РПЗУ-УФ, а транзисторы с двойным затвором пригодны для применения как в

РПЗУ-УФ, так ив РПЗУ-ЭС. Рассмотрим

более современный тип – ЛИЗМОП-тр-р с двойным затвором, приведенный на рис. 20.

Рис.

20. ЛИЗМОП-тр-р с двойным затвором

Принцип работы ЛИЗМОП с двойным затвором близок к

принципу работы МНОП-тр-ра. Здесь также между управляющим затвором и областью

канала помещается область, в которую при программировании можно вводить заряд,

влияющий на величину порогового напряжения тр-ра. Только

область введения заряда представляет собой не границу раздела слоев

диэлектрика, а окруженную со всех сторон диэлектриком проводящую область

(обычно из поликр. Si), в

которую, как в ловушку, можно ввести заряд, способный сохранятся в ней в

течении очень длительного времени. Эта область называется плавающим затвором.

Запись информации

При подаче на упр. затвор импульса положительного

напряжения относительно большой амплитуды 20-25В в обратно-смещенных p-n переходах

возникает лавинный пробой.

Часть электронов, имеющих энергию, достаточную для преодоления

потенциального барьера диэлектрической области, проникает в плавающий затвор.

Снятие высокого программирующего напряжения восстанавливает обычное состояние

областей транзистора и запирает электроны в плавающем затворе, где они могут

находиться длительное время (в высококачественных приборах многие годы).

Заряженный электронами плавающий затвор увеличивает пороговое

напряжение транзистора настолько, что в диапазоне рабочих напряжений проводящий

канал в транзисторе не создается.

При отсутствии заряда в плавающем затворе транзистор работает в

обычном ключевом режиме.

Стирание информации может производиться двумя способами –

ультрафиолетовым облучением или электрическими сигналами.

В первом случае корпус ИС имеет

специальное прозрачное окошко для облучения кристалла. Двуокись кремния и

поликремний прозрачны для ультрафиолетовых лучей. Эти лучи

вызывают в областях транзистора фото и тепловые токи, что делает области прибора

проводящими и позволяет зарядам покинуть плавающий затвор. Операция стирания

информации этим способом занимает десятки минут, информация стирается сразу во

всем кристалле. Число циклов перезаписи лежит в пределах от 10 до 100 (что

плохо, т.к. мало).

Электрическое

стирание информации осущ-ся подачей на управл. затворы низкого (нулевого)

напряжения, а на стеки – высокого напряжения программирования. Электрическое

стирание имеет преимущество: можно стирать информацию не со всего кристалла, а

выборочно (индивидуально для каждого адреса).

Длительность

процесса стирания уже не десятки минут, а значительно меньше (250нс - 90нс). Число циклов программирования – 104…106.

Поэтому в настоящее время электрическое стирание почти полностью вытеснило УФ

стирание.

Подключение 2х

затворных ЛИЗМОП-транзисторов к линиям выборки строк и линиям чтения в матрицах

ЗУ имеет следующий вид рис.22

Рис.22

Запись лог.

"0" осуществляется путем заряда плавающего затвора инжекцией

"горячих" электронов в режиме программирования. Стирание информации,

под которым понимается удаление заряда из плавающего затвора, приводит к записи

во все запоминающие элементы лог. единиц, т.к. в данном случае опрашиваемые

тр-ры открываются и передают напряжение Uип на линии считывания.

Импульсное питание ПЗУ

Энергонезависимость

всех ПЗУ, сохраняющих информацию при отключении питания, открывает возможности

экономии питания при их эксплуатации и, соответственно, улучшения их теплового

режима, что повышает надежность схем.

Питание можно

подавать только на те ИМС памяти, к которым в данный момент происходит

обращение.

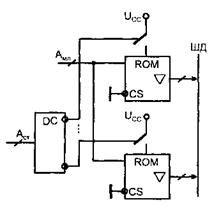

Рассмотрим обычный вариант

построения модуля памяти, состоящего из нескольких ИС, и вариант с импульсным

питанием. В обычном варианте напряжение Uип подключается ко всем ИС

постоянно, а выбор адресуемой ИС осуществляется сигналом CS

(выбор кристалла). В варианте с импульсным питанием работа всех ИС по входам CS

постоянно разрешена, но питание подключается только к выбранной микросхеме с

помощью ключа, управляемого от выходов адресного ДШ. Импульсный режим питания

позволяет многократно уменьшить потребляемую мощность.

Рассмотрим обычный вариант

построения модуля памяти, состоящего из нескольких ИС, и вариант с импульсным

питанием. В обычном варианте напряжение Uип подключается ко всем ИС

постоянно, а выбор адресуемой ИС осуществляется сигналом CS

(выбор кристалла). В варианте с импульсным питанием работа всех ИС по входам CS

постоянно разрешена, но питание подключается только к выбранной микросхеме с

помощью ключа, управляемого от выходов адресного ДШ. Импульсный режим питания

позволяет многократно уменьшить потребляемую мощность.

(а) (б)

Рис. 23.

Модули постоянной памяти с обычным (а) и импульсным (б) питанием

(ФП) (Flash – Memory)

По типу ЗЭ и принципам

работы подобна памяти РПЗУ-ЭС, однако ряд архитектурных и структурных

особенностей позволили выделить ее в отдельный класс. Разработка ФП считается

кульминацией десятилетнего развития схемотехники памяти с электрическим

стиранием информации.

В схемах ФП не

предусмотрено стирание отдельных слоев. Стирание информации осуществляется либо

для всей памяти одновременно, либо для достаточно больших блоков, что позволяет

не только упростить схему ЗУ, но и способствует достижению высокого уровня

интеграции и быстродействия при снижении их стоимости.

ФП обычно

используется при хранении секретных данных, которые при попытке

несанкционированного доступа к ним автоматически мгновенно стираются.

Поэтому название

Flash (англ. миг, мгновение) перешло к памяти, обладающей

свойством быстрого стирания всего массива данных одним сигналом.

Одновременное

стирание всей информации ЗУ реализуется просто, но имеет тот недостаток, что

даже замена одного слова в ЗУ (при записи новой информации), требует стирания и

новой записи для всего ЗУ в целом. Для многих применений это неудобно. Поэтому

наряду со схемами с одновременным стиранием всего содержимого имеются схемы с

блочной структурой, в которых весь массив памяти делится на блоки, стираемые

независимо друг от друга. Объем таких блоков сильно различается (от 256 байт до

128 Кбайт и выше).

Двумя основными

направлениями эффективного использования ФП явл-ся хранение не очень часто

изменяемых данных и замена памяти на магнитных дисках. Среди устр-в с блочным

стиранием выделяют схемы со специализированными блоками (несимметричные блочные

структуры). По имени так называемых Boot-блоков, в которых

информация защищена аппаратными средствами от случайного стирания эти ЗУ наз. Boot Block Flash Memory

(BBFM). Обычно Boot-блоки

хранят программы инициализации системы, позволяющие ввести ее в рабочее

состояние после включения питания.

Микросхемы для

замены жестких магнитных дисков (Flash – File Memory)

содержат более развитые средства перезаписи информации и имеют идентичные блоки

(симметричные блочные структуры).

Элементом

структуры Флэш-памяти явл-ся накопитель (матрица ЗЭ). В схемотехнике НК

используются ячейки на основе ЛЭ ИЛИ-НЕ, И-НЕ. НК на основе ячеек ИЛИ-НЕ (с

параллельным включением ЛИЗМОП с двойным затвором) обеспечивают быстрый доступ

к словам при произвольной выборке.

Структура

матрица накопителя ФП (с параллельным включением ЛИЗМОП) имеет следующий вид

рис.24

Рис.24. Структура матрицы

накопителя ФП на основе ячеек ИЛИ-НЕ.

В этой схеме каждый столбец представляет собой

совокупность параллельно соединенных транзисторов. Все транз-ры невыбранных

строк заперты. В выбранной строке открываются и передают высокий уровень

напряжения на разрядные линии считывания те тр-ры, в плавающих затворах которых

отсутствует заряд электронов, и, сл-но, пороговое напряжение тр-в имеет

нормальное (не повышенное) значение.

НК на основе

ячеек ИЛИ-НЕ широко исполь-ся фирмой Intel. В настоящее время идут

разработки, связанные с заменой жестких магнитных дисков Флэш-памятью (что дает

возможность отказаться от мех. жестких дисков).

Файловая Флэш-память (ФФП)

В течение многих

лет хранение больших объемов данных возлагались в ЭВМ на хорошо отработанные и

сравнительно недорогие внешние ЗУ на магнитных, а в последствии и оптических

дисках.

Во многих

компьютерах система памяти организована как сочетание жесткого магнитного диска

(винчестера) с динамическим полупроводниковым ОЗУ. Имея значительные

достоинства, дисковые ЗУ как электромеханическиее устр-ва не свободны от ряда

недостатков: например, чувствительность к ударам, вибрациям и загрязнениям,

ограниченное быстродействие и значительная потребляемая мощность. Эти

недостатки особенно сказываются в портативных устр-х с автономным (батарейным)

питанием.

Например:

дисководы потребляют мощность около 3 Вт, что в системах с напряжением питания

3,3 … 5 В означает потребление токов 0,6 … 0,9 Ф, быстро истощающих батарейки.

ФФП ориентирована на замену твердых дисков, которая в сотни раз сокращает

потребляемую мощ-ть, в той же мере увеличивает механическую прочность и надежность

ЗУ, уменьшает их размеры и вес, на несколько порядков повышает быстродействие

при чтении данных, сохраняя при этом программную совместимость со средствами

управления памятью. Вместе с тем за дисковой памятью остаются преимущества по

информационной емкости и стоимости (ФФП

фирмы Intel: инф.

емк. 4-16 Мбит;

Uип – 5; 3,3; 2,7 В; разрядность – 8, 16; tсчит – 70-150 нс)

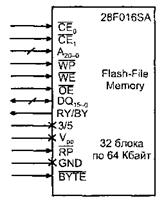

Рис. 25. Внешняя организация

файловой Флэш-памяти (на примере ИС 28F016SA Intel)

Шина

адреса: линии А20-16 выбирают один из блоков, линии А15-1

выбирают слово в пределах одного блока (блок с емкостью 64 Кбайта содержит 32

Кслов), линия A0 — бит выборки байта, определяющий старший

и младший байты при байтовой организации памяти и отключаемый при ее словарной

организации. От процессора поступает начальный адрес блока данных, который

запоминается в очереди адресов. Текущий адрес ячейки памяти для обмена

формируется адресным счетчиком.

В

шине данных DQ15-0 линии DQ7-0 предназначены для ввода и

вывода младшего байта данных, передачи команды в командный интерфейс

пользователя CUI в цикле записи и вывода данных из буфера, регистров

идентификатора или состояния в соответствующих режимах чтения. Линии DQ15-8

предназначены для передачи старшего байта при словарной организации памяти. По

ним выводят данные накопителя, буфера или идентификатора в соответствующем

режиме чтения, но эти линии не используются для чтения из регистров состояния.

Если кристалл не выбран или запрещен вывод, линии шины данных переходят в

третье состояние.

Линии CE0 и CE1 — входы разрешения кристалла, при высоком уровне любого из

них кристалл не выбран, и потребление мощности снижается до уровня состояния

покоя (Standby) после завершения текущей операции записи или стирания.

Линии CE0 и CE1 — входы разрешения кристалла, при высоком уровне любого из

них кристалл не выбран, и потребление мощности снижается до уровня состояния

покоя (Standby) после завершения текущей операции записи или стирания.

Сигнал ОЕ

открывает выходные буферы при низком уровне и переводит их в третье состояние

при высоком.

Сигнал ОЕ

открывает выходные буферы при низком уровне и переводит их в третье состояние

при высоком.

Сигнал WE

управляет доступом к командному интерфейсу пользователя CUI, страничным

буферам, регистрам очереди данных и защелкам очереди адресов.

Сигнал WE

управляет доступом к командному интерфейсу пользователя CUI, страничным

буферам, регистрам очереди данных и защелкам очереди адресов.

Сигнал RP (Reset/Power-Down) при низком уровне

вводит схему в состояние глубокой экономии мощности, отключая все схемы,

потребляющие статическую мощность. При выходе из этого состояния время

восстановления схемы составляет 400 не. При переходе к низкому уровню операции

автомата записи прекращаются, схема сбрасывается.

Сигнал RY/BY

(Ready/Busy) индицирует состояние внутреннего автомата записи. Низкий уровень

означает занятость, высокий (кстати говоря, сигнал вырабатывается каскадом с

открытым стоком, требующим подключения внешней цепочки Uип — R для

формирования высокого уровня) означает или готовность к новым операциям, или

приостановление стирания, или состояние глубокой экономии мощности в

зависимости от выполняемой операции.

Сигнал RY/BY

(Ready/Busy) индицирует состояние внутреннего автомата записи. Низкий уровень

означает занятость, высокий (кстати говоря, сигнал вырабатывается каскадом с

открытым стоком, требующим подключения внешней цепочки Uип — R для

формирования высокого уровня) означает или готовность к новым операциям, или

приостановление стирания, или состояние глубокой экономии мощности в

зависимости от выполняемой операции.

Сигнал WP (Write

Protect) имеет следующий смысл. Каждый блок имеет бит запрещения записи (Lock-bit).

Низкий уровень WP разрешает защиту, т. е. запись или стирание в блоке могут

выполняться только при Lock-bit = 0. При высоком уровне WP в блоках могут

выполняться операции записи и стирания независимо от состояния блокирующих

битов.

Сигнал WP (Write

Protect) имеет следующий смысл. Каждый блок имеет бит запрещения записи (Lock-bit).

Низкий уровень WP разрешает защиту, т. е. запись или стирание в блоке могут

выполняться только при Lock-bit = 0. При высоком уровне WP в блоках могут

выполняться операции записи и стирания независимо от состояния блокирующих

битов.

Сигнал

BYTE низким уровнем вводит схему в байтовый режим, высоким — в словарный и

выключает буфер линии Ао.

Напряжение программирования и вывод напряжения

питания (это может быть 3,3 или 5 В — вход обозначен дробью 3/5) поступают в

схему через переключатель напряжения, который находится внутри схемы.

Умножение в АЛУ двоичных

чисел.

Как известно,

операция умножения в ЭВМ с помощью соответствующих алгоритмов сводится к

выполнению операций сложения и сдвига.

Существует

четыре метода умножения. Наиболее распространенный метод умножения целых чисел

– начиная с младшего разряда со сдвигом суммы частичных произведений вправо при

неподвижном множимом, как показано на рис. 26

Рис. 26

Операция состоит

из n циклов (n – число цифровых разрядов

множителя). В каждом цикле анализируется очередная цифра множителя, и если это

1, то к сумме частичных произведений относительно неподвижного множителя (если

не выполн-ся умножение на знаковый разряд).

Регистр

множителя и сумматор частичных произведений при этом должны иметь цепи сдвига

вправо.

Схема АЛУ для

умножения n-разрядный положительных двоичных чисел приведена на рис. 27.

Рис. 27. Схема АЛУ для

умножения целых n-разрядных положительных двоичных чисел.

Рис. 28. Микропрограмма

выполн. операций умножения целых положительных чисел.

Работа АЛУ при умножении целых положительных чисел описывается

микропрограммой, приведенной на рис. 28.

Первоначально в

Рг1 поступает множимое. Регистр РгВ, хранящий сумму частичных произведений,

устанавливается в нулевое состояние, а в счетчик циклов СчЦ заносится число

обрабатываемых цифровых разрядов (блок 1). Затем в Рг2 поступает множитель

(блок 2). На этом завершается процедура начальных установок и начинается

процесс вычисления сумм частичных произведений. В зависимости от

значений (0 или 1) младшего разряда множителя к частичному произведению

прибавляется либо "0", либо "X", для чего регистру

РгА сумматора присваивается соответствующее значение. Полученная сумма

умножается на 2-1 путем передачи кода с выхода сумматора на РгСМ со

сдвигом на один разряд вправо. Одновременно множитель подготавливается к

перемещению в Рг2 так, чтобы на месте анализируемого младшего разряда в Рг2

оказался следующий разряд множителя. Для этого содержимое регистра Рг2

передается в регистр Рг2' со сдвигом вправо на один разряд.

Один разряд рег.

Рг2' при этом остается свободным и в него заносится младший разряд суммы,

выходящий при сдвиге за пределы регистра РгСМ (Рг2'[0]:=СМ[n-1]). В

следующем такте (блок 5) завершается сдвиг множителя путем занесения

содержимого регистра Рг2' в регистр Рг2 и в регистр РгВ образуется сдвинутая

сумма частичных произведений.

Кроме того, в

этом такте уменьшается на 1 содержимое счетчика циклов. Когда счетчик циклов

достигает нуля, в регистрах РгСМ м Рг2 будут храниться соответственно старшие и

младшие разряды произведения, требующие сдвига на один разряд вправо для

правильного расположения в формате двойного слова. После выполнения этих

сдвигов (блоки 6 и 7) результат операции из РгСМ и Рг2 поступает на ШИ Вых

(микрооперация выдачи произведения на ШИ Вых на рис. не показаны).

Деление в АЛУ двоичных чисел

Рис. 29. Схема АЛУ для

деления двоичных чисел, представленных в форме с фиксированной точкой без

восстановления остатка

Алгоритм деления

без восстановления остатка следующий:

1. Из

предварительно сдвинутого в сторону старших разрядов делимого вычесть делитель.

2. Остаток

увеличить сдвигом влево.

3. Если остаток

положительный, то делитель вычесть из остатка, а если отрицательный, то

делитель сложить с остатком.

4. Если

полученный остаток положительный, то цифре частного присвоить значение 1, если

отрицательный, то цифре частного присвоить значение "0".

5. Повторить

действия п. 1, в которых место делимого занимает полученный остаток.

Действия

повторяются до тех пор, пока не будут выработаны все последующие цифры

частного.

Схема

представлена на рис. 29, где:

СхУ – схема

управления,

РгД – регистр

делителя,

РгЧ – регистр

частного.

В исходном

состоянии в сумматор СМ заносится делимое в модифицированном обратном коде, а в

регистр делителя – делитель. Регистр суммы устанавливается в нулевое состояние.

Операция начинается со сдвига делимого. Если знак остатка окажется

положительным, то формируется сигнал переполнения "У" и деление не

производится.

Если знак

остатка окажется положительным, то формируется сигнал переполнения У и деление

не производится. Если знак остатка отрицат., то начинается последовательная

выработка "m" цифр частного. На каждом шаге деления

положительный или отрицат. делитель записывается в сумматор в модифицированном

коде. Знак делителя определяется знаком остатка, находящегося в знаковом

разряде сумматора на данный момент времени. Если в этом разряде стоит 1, то

схема управления выдает сигнал Sпр на запись положит. делителя

в сумматор и делитель через n схем И1. Если же

в знаковом разряде стоит "0", то выдается сигнал Sобр и в сумматор СМ через n схем И2

с добавлением 1 в младший разряд сумматора СМ записывается отрицательный

делитель.

В первом и втором случаях в сумматоре производится

сложение кодов остатка и делителя и образование нового остатка. По знаку нового

остатка определяется значение очередного разряда частного: если знак

положительный, в младший разряд регистра частного заносится "1", если

знак отрицательный – заносится "0". После этого остаток удваивается,

для чего оно сдвигается на один разряд в сторону старших разрядов. Одновременно

сдвигается и содержимое регистра частного, освобождая младший разряд для приема

очередного разряда частного.

Цифроаналоговые

преобразователи ЦАП и аналогово-цифровые преобр-ли АЦП в основном используются

для сопряжения цифровых устр-в и систем с внешними аналоговыми сигналами, т.е.

АЦП преобразует аналоговые сигналы в цифровые, а ЦАП цифровые в аналоговые

сигналы. Например, датчик анал. сигналов через АЦП сопрягается с цифровым

устр-м (ЭВМ и т.п.).

ЦАП и АЦП широко

применяются:

- в

измерительной технике (это цифровые осциллографы, вольтметры, генераторы

сигналов и т.п.),

- в компьютерной

технике (это ввод и вывод звука в компьютерах, видеомониторы, принтеры), а

также

- в телефонии,

радио и гидролокации.

АЦП и ЦАП

выпускаются в виде специализированных микросхем.

ЦАП

Микросхемы ЦАП

можно представить в виде блока (n входов и один аналоговый

выход).

Рис. 30

На входы D0…Dn-1 подается n-разрядный

код N, а на аналоговый вход Uоп – опорное напряжение.

Выходным

сигналом является напряжением Uвых (Uо) или вых. ток Iвых (Iо). При этом вых. ток или вых.

напр. пропорциональны входному току и опорному напряжению.

Для одних ИМС Uоп имеет строго заданный

уровень, для других допускается изменять Uоп в широких пределах (в том

числе и менять его полярность – пол. на отриц. И наоборот).

Схема

преобразования Io в вых. напр. Uвых приведена на рис. 31.

Рис. 31. Преобразование Iвых в Uвых с помощью операционного

усилителя.

Идея

преобразования входного цифрового кода N в выходной аналоговый

сигнал состоит в суммировании нескольких токов, каждый последующий из которых

вдвое больше предыдущего.

Для получения

этих токов используются резистивные матрицы (или транзисторные источники тока),

коммутируемые транзисторными ключами.

В качестве

примера рассмотрим схему реализации 4х-разрядного цифро-аналогового

преобразователя на основе резистивной матрицы типа R-2R и ключей (транзисторные

ключи для управления представлены в виде переключателей.)

Правому

положению ключа соответствует единица в данном разряде кода N (D0…D3).

Как уже

отмечалось выше, операционный усилитель может быть как встроенным (в случае ЦАП

с выходом по напряжению), так и внешним (в случае ЦАП с выходом по току)

(токовый выход малоинерционен).

Первым (левым)

ключом N1 коммутируется ток величиной I1=Uоп/2R, вторым ключом ток I2=Uоп/4R и т.д. (I1=Uоп/2R; I2=Uоп/4R; I3=Uоп/8R; I4=Uоп/16R), т.е. токи, коммутируемые

соседними ключами, различаются вдвое, как и веса разрядов двоичного кода 20,

21, 22, 23.

Схема 4хразр.

ЦАП имеет вид рис. 32:

Рис. 32

Суммарный ток I∑вых от всех ключей создает на

выходе опер. усилителя напряжение Uвых=Iвых∙Rос, т.е. вклад 1го

ключа (старшего разряда кода) в выходное напряжение составляет –Uоп/2, второго –2Uоп/4, третьего –3Uоп/8 и четвертого –4Uоп/16 . Т.о., при входном коде N=0000 Uвых=0, а при входном коде N=1111 вых. напр. будет равно –15Uоп/16

(т.к. 1111 = 15).

В общем случае вых. напр. ЦАП будет связано со входным кодом N и опорным напряжением Uоп

простой формулой

Uвых = –NUоп∙2-n=–NUоп/2n;

для 4хразр. кода Uвых = –NUоп/16,

где n –

кол-во разрядов входного кода. Знак минуса получается из-за инверсии сигнала

операц. усилителем.

Увеличение кол.

разрядов ЦАП более сложная задача, поэтому на практике встречается редко.

Рис. 33

Т.о.,

основное применение ИМС ЦАП состоит в получении аналогового сигнала из

последовательности цифровых кодов N.

Условие

нормальной работы ЦАП состоит в том, чтобы длительность сохранения входного

кода была больше, чем время установления ЦАП – tуст, иначе вых. сигнал не успеет

принять значение, соответствующее входному коду (время установления tуст ЦАП связано с

неидеальностью внутренних элементов ЦАП).

Преобразование

цифровых кодов в аналоговый сигнал – не единственное применение ЦАП. Они могут

использоваться для управляемой обработки аналоговых сигналов, например, для

усиления или ослабления аналоговых сигналов в заданное число раз.

Для этого лучше

всего подходят умножающие ЦАП, которые допускают изменение уровня опорного

напряжения в широких пределах, в том числе и с изменением его знака (такие ИМС

ЦАП выпускаются серийно).

Простейшая схема

этой серии – это цифровой аттенюатор цифрового сигнала.

Аттенюатор

аналогового сигнала на ЦАП имеет вид:

Рис. 34

В этой схеме

вместо постоянного опорного напряжения подается переменный аналоговый сигнал. Выходной сигнал связан со

входным простой формулой Uвых = -Uвх ∙ N

∙ 2-n. Т.е. вых. сигнал

пропорционален входному (с инверсией), а коэф. пропорциональности определяется

входным цифровым кодом N. Коэф. пропорциональности изменяется от нуля и почти

до единицы с шагом равным 2-n.

Входной регистр RG в

данном случае также необходим, т.к. при неодновременном переключении разрядов

входного кода на вых. сигнал ЦАП могут накладываться короткие импульсы

значительной амплитуды.

Схема

включения ЦАП, используемого как усилитель аналогового сигнала с коэф. усиления,

задаваемым входным кодом N, имеет след. вид рис. 35:

Рис. 35

В этом случае

вых. ток ЦАП равен величине Iвых=Uвх/Rос, а так как в качестве

опорного напр. используется вых. напр., то получается, что вых. напр. связано

со вх. напр. формулой

Uвых = -Uвх ∙ 2n/N = (-Uвх ∙ 2n)/N;

т.е. коэфф.

пропорциональности между вых. и вх. напряжениями обратно пропорционален коду N. Код N может

меняться в этом случае от 1 до (2n-1), что соотв. коэфф.

усиления ≈ от 1 до 2n.

Например, при

10разрядном ЦАП коэфф. усиления схемы может достигать 210=1024.

Используя ЦАП,

можно построить схему сдвига аналогового сигнала на величину, задаваемую

входным цифровым кодом. Сдвиг представляет собой, по сути, сложение аналогового

сигнала с постоянным напряжением.

АЦП

Условное графическое обозначение АЦП имеет след. вид:

Рис. 36

В целом АЦП представляет собой устройства,

предназначенные для преобразования электрических величин (напряжения, тока,

мощности, сопротивления, емкости и т.д.) в цифровой код. Наиболее часто входной

величиной АЦП явл. напряжение.

Все другие

электрические величины перед подачей на АЦП необходимо предварительно

преобразовывать в напряжение.

При

преобразовании напряжения в цифровой код используются три независимые операции:

дискретизация, квантование кодирование.

Дискретизация

представляет собой преобразование непрерывных функций напряжения U(t) в U(tn), отнесенных к некоторым фиксированным моментам времени ti. Т.о., при дискретизации непрерывная функция U(t) преобразуется в

последовательность ее отчетов U(tn)

2. Вторая

операция, называемая квантованием, состоит в том, что мгновенные значения

функции U(ti) ограничиваются только

определенными уровнями, которые назыв. уровнями квантования. В результате

квантования непрерывная функция U(ti) принимает вид ступенчатой

кривой Uk(t)

3. Третья

операция назыв. кодированием, в процессе которого дискретные квантованные

величины преобразуются в цифровой код, т.е. последовательность цифр,

подчиненных определенному закону.

Т.о. выходной

величиной АЦП явл. цифровой код, т.е. последовательность цифр, с помощью

которой представляются дискретные квантованные величины.

Большинство АЦП

работают с выходом в натуральном двоичном коде, при котором каждому

положительному числу N ставится в соответствие код {bi}=b1b2…bn, где bi равны нулю или единице.

Принципы построения АЦП

По признаку

измеряемого значения напряжения АЦП делятся на две группы:

АЦП мгновенных

значений напряжения и АЦП средних значений напряжения (интегрирующие АЦП)

АЦП, которые

позволяют определять код мгновенного значения напряжения, можно также разделить

на АЦП последовательного и параллельного счета, а также

параллельно-последовательного счета.

Схема АЦП

последовательного счета имеет след. вид рис.37

Рис. 37

Схема АЦП

состоит из компаратора, сравнивающего Uвх с напряжением обратной

связи U5. На прямой вход компаратора поступает входной сигнал Uвх, а на инвертирующий –

напряжение обратной связи U5.

Работа

преобразователя начинается с приходом импульса "Пуск" от схемы

управления, который замыкает ключ S. Через замкнутый ключ S

импульсы U1 от генератора тактовых импульсов поступают на счетчик,

который управляет работой ЦАП (U3).

В результате

последовательного увеличения выходного кода счетчика N происходит последовательное

ступенчатое увеличение выходного напряжения U5 ЦАП. Питание ЦАП

осуществляется от источника опорного напряжения U4.

Когда вых. напр.

ЦАП U5 сравнивается со входным напряжением, происходит переключение

компаратора и по его выходному сигналу "Стоп" размыкается ключ S. В

результате импульсы от генератора перестанут поступать на вход счетчика.

Выходной код,

соответствующий равенству Uвх=U5 снимается с выходного

регистра счетчика.

Max время преобразования АЦП опред-ся по формуле Tпр=(2n-1)T, где n –

число двоичных разрядов счетчика, T – период следования счетных

импульсов (опред. Частотой генератора тактовых импульсов).

Например: при n = 10

разрядов и T = 1 мкс (т.е. тактовая частота генератора равна 1 МГц) max.

Время преобразования равно

Tпр=(210-1)∙1≈1024мкс≈1мс,

что обеспечивает max

частоту преобразования около 1 кГц.

Структурная

схема параллельного АЦП имеет след. вид рис. 38.

В этой схеме

преобразователь осуществляет одновременное квантование входного сигнала Uвх с помощью набора

компараторов, включенных параллельно источнику сигнала.

Рис. 38

Пороговые уровни

компараторов установлены с помощью резистивного делителя в соответствии с

используемой шкалой квантования.

При подаче на

входы компараторов сигнала Uвх на их выходах получим

квантованный сигнал.

При работе в

двоичном коде все резисторы делителя имеют одинаковые сопротивления R.

Время

преобразования такого преобразователя составляет один такт, т.е. Tпр=T. Параллельные

преобразователи явл. в настоящее время самыми быстрыми и могут работать с

частотой дискретизации свыше 100 МГц.

Делитель

опорного напряжения представляет собой набор низкоомных резисторов с

сопротивлением около 1 Ом.

Типовая задержка

срабатывания компараторов около 7 нс.

По выводу

коррекции осуществляется коррекция напряжения смещения нулевого уровня на входе

АЦП, а по выводу Uоп осущ. регулировка погрешности преобразования.

Рис. 39. Схема 3хразрядного

параллельного АЦП

Резистивный

делитель из 2n одинаковых резисторов делит опорное напряжение на (2n-1)

уровней.

Входное напряжение

сравнивается с уровнями, формируемыми делителем напряжения. Вых. сигналы

компараторов с помощью шифраторов преобразуются в n-разрядный двоичный код.

Рис.

1

Рис.

1